**INF8574**

#### **GENERAL DESCRIPTION**

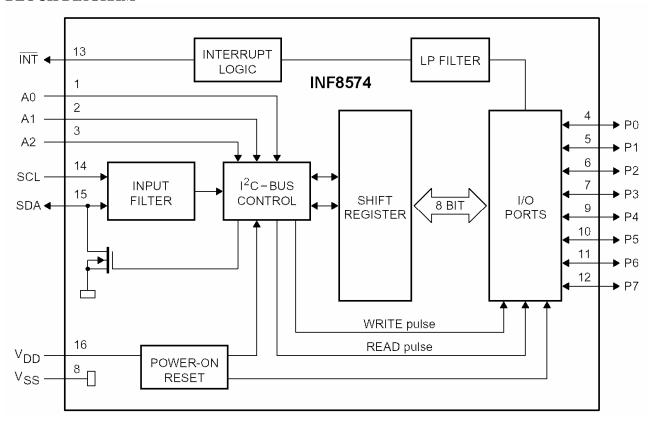

The INF8574 is a silicon CMOS circuit. It provides general purpose remote I/O expansion for most microcontroller families via the two-line bidirectional bus (I<sup>2</sup>C).

The device consists of an 8-bit quasi-bidirectional Port and an I<sup>2</sup>C interface. The INF8574 has a low current consumption and includes latched outputs with high current drive capability for directly driving LEDs. It also possesses an interrupt line (INT) which can be connected to the interrupt logic of the microcontroller. By sending an interrupt signal on this line, the remote I/O can inform the microcontroller if there is incoming data on its ports without having to communicate via the I<sup>2</sup>C-bus. This means that the INF8574 can remain a simple slave device.

## **FEATURES**

Operating supply voltage 2.5 to 6 V

Low standby current consumption of 10 A maximum

I<sup>2</sup>C to parallel port expander

Open-drain interrupt output

8-bit remote I/O Port for the I<sup>2</sup>C-bus

Compatible with most microcontrollers

Latched outputs with high current drive capability for directly driving LEDs

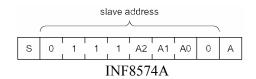

Address by 3 hardware address pins for use of up to 8 devices (up to 16 with INF8574A)

DIP16, space-saving SO16 or SSOP20 package.

### **BLOCK DIAGRAM**

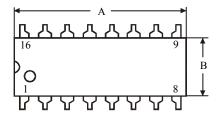

#### **PINNING**

| SYMBOL          | PIN | DESCRIPTION                    |                   |         |                    |

|-----------------|-----|--------------------------------|-------------------|---------|--------------------|

| A0              | 1   | address input 0                | A0 1              | $\circ$ | 16 V <sub>DD</sub> |

| A1              | 2   | address input 1                |                   |         |                    |

| A2              | 3   | address input 2                | A1 2              |         | 15 SDA             |

| P0              | 4   | quasi-bidirectional I/O Port 0 |                   |         |                    |

| P1              | 5   | quasi-bidirectional I/O Port 1 | A2 3              |         | 14 SCL             |

| P2              | 6   | quasi-bidirectional I/O Port 2 |                   |         |                    |

| P3              | 7   | quasi-bidirectional I/O Port 3 | P0 4              |         | 13 <u>INT</u>      |

| <sup>v</sup> SS | 8   | supply ground                  |                   | INF8574 |                    |

| P4              | 9   | quasi-bidirectional I/O Port 4 | P1 5              |         | 12 P7              |

| P5              | 10  | quasi-bidirectional I/O Port 5 |                   |         |                    |

| P6              | 11  | quasi-bidirectional I/O Port 6 | P2 6              |         | 11 P6              |

| P7              | 12  | quasi-bidirectional I/O Port 7 |                   |         |                    |

| INT             | 13  | interrupt output (active LOW)  | P3 7              |         | 10 P5              |

| SCL             | 14  | serial clock line              |                   |         |                    |

| SDA             | 15  | serial data line               | V <sub>SS</sub> 8 |         | 9 P4               |

| <sup>V</sup> DD | 16  | supply voltage                 | L                 |         | J                  |

## CHARACTERISTICS OF THE I<sup>2</sup>C-BUS

The I<sup>2</sup>C-bus is for 2-way, 2-line communication between different ICs or modules. The two lines are a serial data line (SDA) and a serial clock line (SCL). Both lines must be connected to a positive supply via a pull-up resistor when connected to the output stages of a device. Data transfer may be initiated only when the bus is not busy.

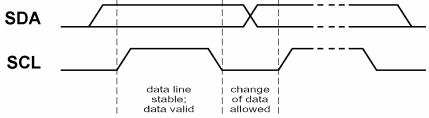

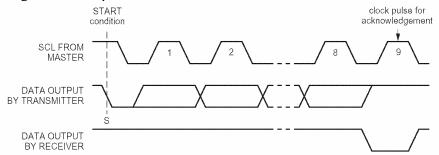

### Bit transfer

One data bit is transferred during each clock pulse. The data on the SDA line must remain stable during the HIGH period of the clock pulse as changes in the data line at this time will be interpreted as control signals

## Bit transfer.

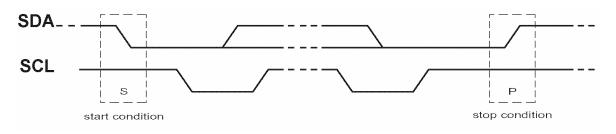

Both data and clock lines remain HIGH when the bus is not busy. A HIGH-to-LOW transition of the data line, while the clock is HIGH is defined as the start condition (S). A LOW-to-HIGH transition of the data line while the clock is HIGH is defined as the stop condition (P).

Definition of start and stop conditions.

## **System configuration**

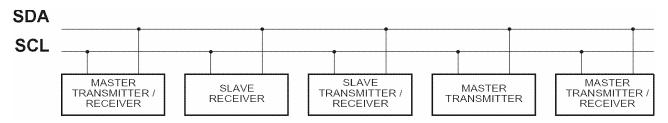

A device generating a message is a 'transmitter', a device receiving is the 'receiver'. The device that controls the message is the 'master' and the devices which are controlled by the master are the 'slaves'.

System configuration.

## Acknowledge

The number of data bytes transferred between the start and the stop conditions from transmitter to receiver is not limited. Each byte of eight bits is followed by one acknowledge bit. The acknowledge bit is a HIGH level put on the bus by the transmitter whereas the master generates an extra acknowledge related clock pulse.

A slave receiver which is addressed must generate an acknowledge after the reception of each byte. Also a master must generate an acknowledge after the reception of each byte that has been clocked out of the slave transmitter. The device that acknowledges has to pull down the SDA line during the acknowledge clock pulse, so that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse, set-up and hold times must be taken into account.

A master receiver must signal an end of data to the transmitter by **not** generating an acknowledge on the last byte that has been clocked out of the slave. In this event the transmitter must leave the data line HIGH to enable the master to generate a stop condition.

Acknowledgement on the  $I^2C$ -bus.

### **FUNCTIONAL DESCRIPTION**

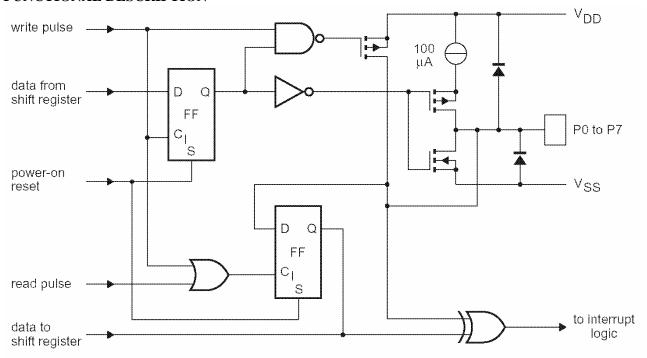

# Simplified schematic diagram of each Port. Addressing

## Slave addresses.

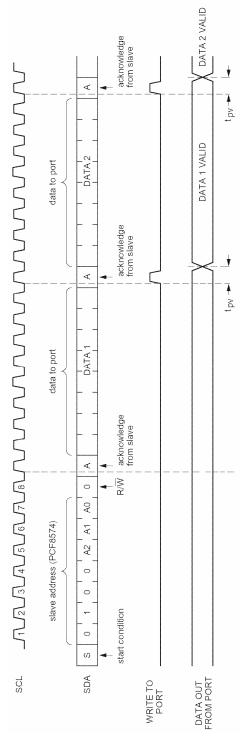

Each bit of the INF8574 I/O Port can be independently used as an input or output. Input data is transferred from the Port to the microcontroller by the READ mode (see Fig.11). Output data is transmitted to the Port by the WRITE mode (see Fig.10).

WRITE mode (output Port).

A LOW-to-HIGH transition of SDA, while SCL is HIGH is defined as the stop condition (P). Transfer of data can be stopped at any moment by a stop condition. When this occurs, data present at the last acknowledge phase is valid (output mode). Input data is lost.

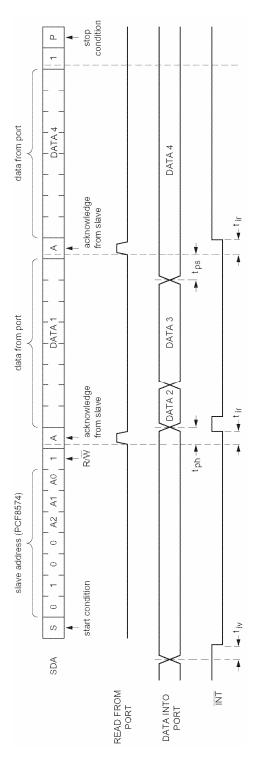

READ mode (input Port).

## **Interrupt**

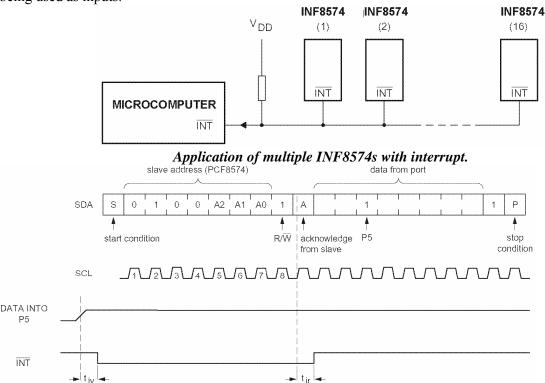

The INF8574 provides an open drain output (INT) which can be fed to a corresponding input of the microcontroller. This gives these chips a type of master function which can initiate an action elsewhere in the system.

An interrupt is generated by any rising or falling edge of the Port inputs in the input mode. After time  $t_{iv}$  the signal INT is valid.

Resetting and reactivating the interrupt circuit is achieved when data on the Port is changed to the original setting or data is read from or written to the Port which has generated the interrupt.

Resetting occurs as follows:

In the READ mode at the acknowledge bit after the rising edge of the SCL signal. In the WRITE mode at the acknowledge bit after the HIGH-to-LOW transition of the SCL signal. Interrupts which occur during the acknowledge clock pulse may be lost (or very short) due to the resetting of the interrupt during this pulse.

Each change of the Ports after the resettings will be detected and after the next rising clock edge, will be transmitted as INT. Reading from or writing to another device does not affect the interrupt circuit.

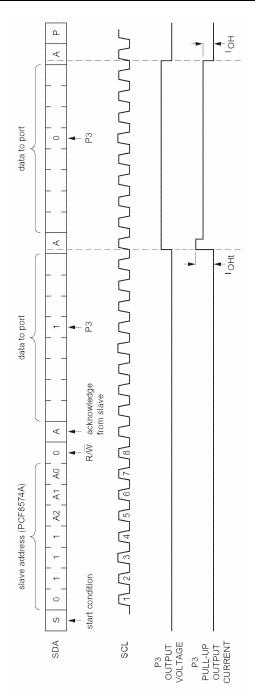

## Quasi-bidirectional I/O Ports

A quasi-bidirectional Port can be used as an input or output without the use of a control signal for data direction. At power-on the Ports are HIGH. In this mode only a <sup>current source to V</sup>DD is active. An additional strong pull-up <sup>to V</sup>DD allows fast rising edges into heavily loaded outputs. These devices turn on when an output is written HIGH, and are switched off by the negative edge of SCL. The Ports should be HIGH before being used as inputs.

Interrupt generated by a change of input to Port P5.

Transient pull-up current  $I_{OHt}$  while P3 changes from LOW-to-HIGH and back to LOW.

# LIMITING VALUES

| SYMBOL      | PARAMETER                     | MIN.                  | MAX.           | UNIT |

|-------------|-------------------------------|-----------------------|----------------|------|

| $V_{ m DD}$ | supply voltage                | -0.5                  | +7.0           | V    |

| $V_{I}$     | input voltage                 | V <sub>SS</sub> - 0.5 | $V_{DD} + 0.5$ | V    |

| $I_{I}$     | DC input current              | -                     | ±20            | mA   |

| $I_{O}$     | DC output current             | -                     | ±25            | mA   |

| $I_{ m DD}$ | supply current                | -                     | ±100           | mA   |

| $I_{SS}$    | supply current                | -                     | ±100           | mA   |

| $P_{tot}$   | total power dissipation       | -                     | 400            | mW   |

| $P_{O}$     | power dissipation per output  | ~-                    | 100            | mW   |

| $T_{stg}$   | storage temperature           | 65                    | +150           | °C   |

| $T_{amb}$   | operating ambient temperature | 40                    | +85            | °C   |

**DC CHARACTERISTICS**  $V_{DD} = 2.5$  to 6 V;  $V_{SS} = 0$  V;  $T_{amb} = 40$  to +85 °C; unless otherwise specified.

| SYMBOL                     | PARAMETER                                        | CONDITIONS                                                                        | MIN.         | TYP.     | MAX.           | UNIT |

|----------------------------|--------------------------------------------------|-----------------------------------------------------------------------------------|--------------|----------|----------------|------|

| Supply                     | •                                                |                                                                                   |              | <u> </u> |                | •    |

| $ m V_{DD}$                | supply voltage                                   |                                                                                   | 2.5          |          | 6.0            | V    |

| $ m I_{DD}$                | supply current                                   | operating mode; $V_{DD} = 6 \text{ V}$ ;<br>no load; $V_I = V_{DD}$ or $V_{SS}$ ; |              | 40       | 100            | μΑ   |

|                            |                                                  | $f_{SCL} = 100 \text{ kHz}$                                                       |              |          |                |      |

| $I_{stb}$                  | standby current                                  | standby mode; $V_{DD} = 6 \text{ V}$ ;<br>no load; $V_I = V_{DD}$ or $V_{SS}$     |              | 2.5      | 10             | μА   |

| $V_{POR}$                  | power-on reset voltage                           | $V_{DD} = 6 \text{ V}$ ; no load;<br>$V_{I} = V_{DD} \text{ or } V_{SS}$ ; note 1 |              | 1.3      | 2.4            | V    |

| Input SCL; in              | put/output SDA                                   | ·                                                                                 |              | <u> </u> |                |      |

| $V_{\rm IL}$               | LOW level input voltage                          |                                                                                   | -0.5         |          | $+0.3V_{DD}$   | V    |

| $V_{IH}$                   | HIGH level input voltage                         |                                                                                   | $0.7V_{DD}$  |          | $V_{DD} + 0.5$ | V    |

| $I_{OL}$                   | LOW level output current                         | $V_{OL} = 0.4 \text{ V}$                                                          | 3            |          |                | mA   |

| $ I_L $                    | leakage current                                  | $V_I = V_{DD}$ or $V_{SS}$                                                        |              |          | 1              | μΑ   |

| $C_{I}$                    | input capacitance                                | $^{V}I = ^{V}SS$                                                                  |              |          | 7              | pF   |

| I/O Ports                  |                                                  |                                                                                   | •            | •        | •              |      |

| $V_{\rm IL}$               | LOW level input voltage                          |                                                                                   | -0.5         |          | $+0.3V_{DD}$   | V    |

| $V_{IH}$                   | HIGH level input voltage                         |                                                                                   | $-0.7V_{DD}$ |          | $V_{DD} + 0.5$ | V    |

| I <sub>IHL(max)</sub>      | maximum allowed input current through protection | $V_1 \ge V_{DD}$ or $V_1 \le V_{SS}$                                              |              |          | ±400           | μΑ   |

| Ť                          | diode LOW level output current                   | V - 1 V: V - 5 V                                                                  | 10           | 25       | +              | mA   |

| I <sub>OL</sub>            | HIGH level output current                        | $V_{OL} = 1 \text{ V}; V_{DD} = 5 \text{ V}$ $V_{OH} = V_{SS}$                    | 30           | 23       | 300            | μA   |

| $ m I_{OH}$ $ m I_{OHt}$   | transient pull-up current                        | HIGH during acknowledge (see Fig.14); $V_{OH} = V_{SS}$                           | 50           | 1        | 300            | mA   |

| ~                          |                                                  | $V_{DD} = 2.5 \text{ V}$                                                          |              |          | 10             |      |

| C <sub>I</sub>             | input capacitance                                |                                                                                   |              |          | 10             | pF   |

| Co                         | output capacitance                               |                                                                                   |              |          | 10             | pF   |

| Port timing C <sub>L</sub> |                                                  |                                                                                   |              |          | L              |      |

| t <sub>pv</sub>            | output data valid                                |                                                                                   |              |          | 4              | μs   |

| t <sub>su</sub>            | input data set-up time                           |                                                                                   | 0            |          |                | μs   |

| t <sub>h</sub>             | input data hold time                             |                                                                                   | 4            |          |                | μs   |

| Interrupt INT              |                                                  | h.                                                                                |              |          |                |      |

| I <sub>OL</sub>            | LOW level output current                         | $^{V}OL = 0.4 \text{ V}$                                                          | 1.6          |          |                | mA   |

| $ I_L $                    | leakage current                                  | $V_I = V_{DD}$ or $V_{SS}$                                                        |              |          | 1              | μΑ   |

| Timing; $C_L \le 10$       |                                                  |                                                                                   |              |          |                |      |

| <sup>t</sup> iv            | input data valid time                            |                                                                                   |              |          | 4              | μs   |

| <sup>t</sup> ir            | reset delay time                                 |                                                                                   |              |          | 4              | μs   |

| Select inputs A            | 0 to A2                                          |                                                                                   |              | •        | •              |      |

| $V_{IL}$                   | LOW level input voltage                          |                                                                                   | -0.5         |          | $+0.3V_{DD}$   | V    |

| $V_{IH}$                   | HIGH level input voltage                         |                                                                                   | $0.7V_{DD}$  |          | $V_{DD} + 0.5$ | V    |

| $ I_{LI} $                 | input leakage current                            | pin at V <sub>DD</sub> or V <sub>SS</sub>                                         |              |          | 250            | nA   |

# Note

1. The power-on reset circuit resets the  $I^2C$ -bus logic with  $V_{DD} < V_{POR}$  and sets all Ports to logic 1 (with current source to  $V_{DD}$ )

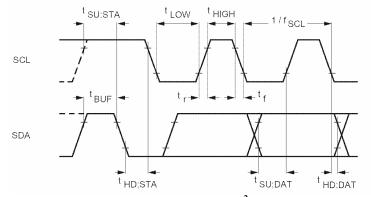

### I<sup>2</sup>C-BUS TIMING CHARACTERISTICS

| SYMBOL                    | PARAMETER                    | MIN.     | TYP. | MAX. | UNIT |

|---------------------------|------------------------------|----------|------|------|------|

| I <sup>2</sup> C-BUS TIMI | ING                          | <u>.</u> |      |      |      |

| $f_{SCL}$                 | SCL clock frequency          |          |      | 100  | kHz  |

| $t_{SW}$                  | tolerable spike width on bus |          |      | 100  | ns   |

| $t_{ m BUF}$              | bus free time                | 4.7      |      |      | μs   |

| t <sub>su;sta</sub>       | start condition set-up time  | 4.7      |      |      | μs   |

| HD;STA                    | start condition hold time    | 4.0      |      |      | μs   |

| LOW                       | SCL LOW time                 | 4.7      |      |      | μs   |

| HIGH                      | SCL HIGH time                | 4.0      |      |      | μs   |

| г                         | SCL and SDA rise time        |          |      | 1.0  | μs   |

| f                         | SCL and SDA fall time        |          |      | 0.3  | μs   |

| SU;DAT                    | data set-up time             | 250      |      |      | ns   |

| HD;DAT                    | data hold time               | 0        |      |      | ns   |

| VD;DAT                    | SCL LOW to data out valid    |          |      | 3.4  | μs   |

| SU;STO                    | stop condition set-up time   | 4.0      |      |      | μs   |

### Note

1. All the timing values are valid within the operating supply voltage and ambient temperature range and refer to  $V_{IL}$  and  $V_{IH}$  with an input voltage swing of  $V_{SS}$  to  $V_{DD}$ .

| PROTOCOL | START<br>CONDITION | BIT 7<br>MSB | BIT 6<br>(A6) |  |

|----------|--------------------|--------------|---------------|--|

|          | (S)                | (A7)         |               |  |

| BIT 0              | ACKNOWLEDGE | STOP      |  |

|--------------------|-------------|-----------|--|

| LSB                | (A)         | CONDITION |  |

| $(R/\overline{W})$ |             | (P)       |  |

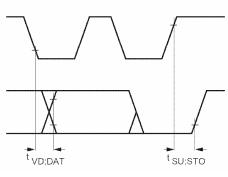

$I^2C$ -bus timing diagram.

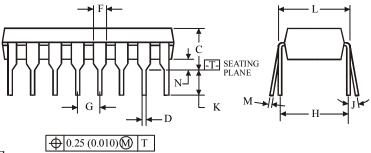

# N SUFFIX PLASTIC DIP (MS - 001BB)

## NOTES:

Dimensions "A", "B" do not include mold flash or protrusions.

Maximum mold flash or protrusions 0.25 mm (0.010) per side.

|        | 1             |       |  |

|--------|---------------|-------|--|

|        | Dimension, mm |       |  |

| Symbol | MIN MAX       |       |  |

| A      | 18.67         | 19.69 |  |

| В      | 6.1           | 7.11  |  |

| C      |               | 5.33  |  |

| D      | 0.36          | 0.56  |  |

| F      | 1.14          | 1.78  |  |

| G      | 2.54          |       |  |

| Н      | 7.            | 62    |  |

| J      | 0°            | 10°   |  |

| K      | 2.92          | 3.81  |  |

| L      | 7.62          | 8.26  |  |

| M      | 0.2           | 0.36  |  |

| N      | 0.38          |       |  |

|        |               |       |  |

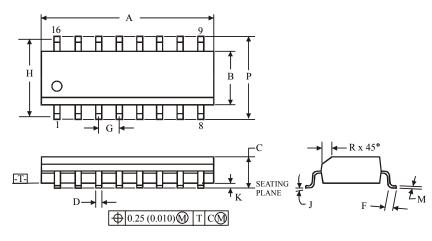

# D SUFFIX SOIC (MS - 012AC)

# NOTES:

- 1. Dimensions A and B do not include mold flash or protrusion.

- 2. Maximum mold flash or protrusion 0.15 mm (0.006) per side for A; for B 0.25 mm (0.010) per side.

|        | Dimension, mm |      |  |

|--------|---------------|------|--|

| Symbol | MIN           | MAX  |  |

| A      | 9.8           | 10   |  |

| В      | 3.8           | 4    |  |

| C      | 1.35          | 1.75 |  |

| D      | 0.33          | 0.51 |  |

| F      | 0.4           | 1.27 |  |

| G      | 1.27          |      |  |

| Н      | 5.            | 72   |  |

| J      | 0°            | 8°   |  |

| K      | 0.1           | 0.25 |  |

| M      | 0.19          | 0.25 |  |

| P      | 5.8           | 6.2  |  |

| R      | 0.25          | 0.5  |  |